- 您现在的位置:买卖IC网 > Sheet目录1194 > ADP1043AFB100EVALZ (Analog Devices Inc)BOARD EVALUATION ADP1043A 100W

�� �

�

�

�ADP1043A�

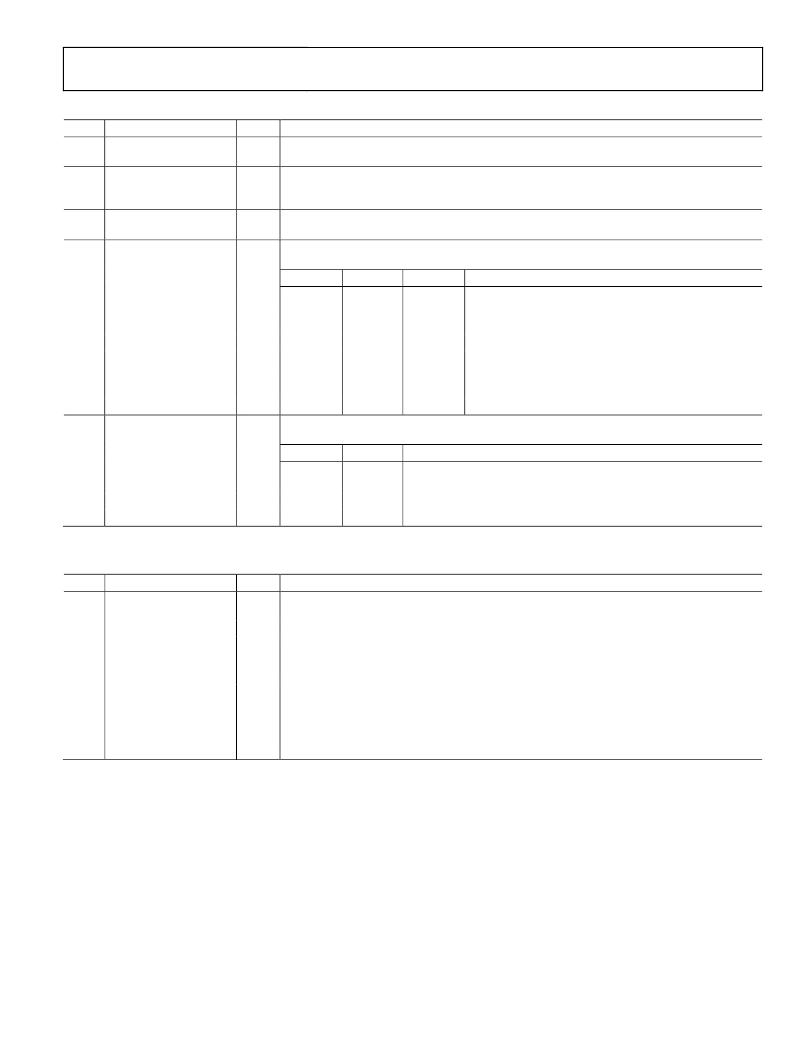

�Table� 14.� Register� 0x0E—Flag� Configuration� Register�

�Bits�

�7�

�Name�

�VDD� OV/VCORE� OV�

�R/W�

�R/W�

�Description�

�Setting� this� bit� means� that� the� VDD� OV� and� VCORE� OV� flags� are� ignored.�

�flags� ignore�

�6�

�VDD� OV/VCORE� OV�

�restart�

�R/W�

�Setting� this� bit� to� 1� means� that� if� the� part� shuts� down,� it� will� download� the� EEPROM� contents�

�again� before� restarting.� Setting� this� bit� to� 0� means� that� if� the� part� shuts� down,� it� will� not�

�download� the� EEPROM� contents� again� before� restarting.�

�5�

�[4:2]�

�VDD� OV/VCORE� OV�

�debounce�

�Accurate� OCP� off� delay�

�for� CS1� and� CS2�

�R/W�

�R/W�

�Setting� this� bit� to� 1� means� that� there� is� a� 500� μs� debounce� before� the� part� shuts� down.� Setting�

�this� bit� to� 0� means� that� there� is� a� 2� μs� debounce� before� the� part� shuts� down.�

�When� an� accurate� OCP� flag� is� set,� there� is� a� delay� before� the� corresponding� action� is� performed.�

�This� delay� is� programmed� using� these� bits.�

�Bit� 4�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�Bit� 3�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�Bit� 2�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�Debounce�

�1.3� ms�

�13� ms�

�130� ms�

�260� ms�

�600� ms�

�1.3� sec�

�2� sec�

�2.6� sec�

�[1:0]�

�Power� supply� reenable�

�time�

�R/W�

�These� bits� specify� the� time� delay� before� restarting� the� power� supply� after� a� shutdown.�

�SR1,� SR2,� and� OrFET� are� reenabled� immediately.�

�Bit� 1�

�Bit� 0�

�Time� (sec)�

�0�

�0�

�0.5�

�0�

�1�

�1�

�1�

�0�

�2�

�1�

�1�

�4�

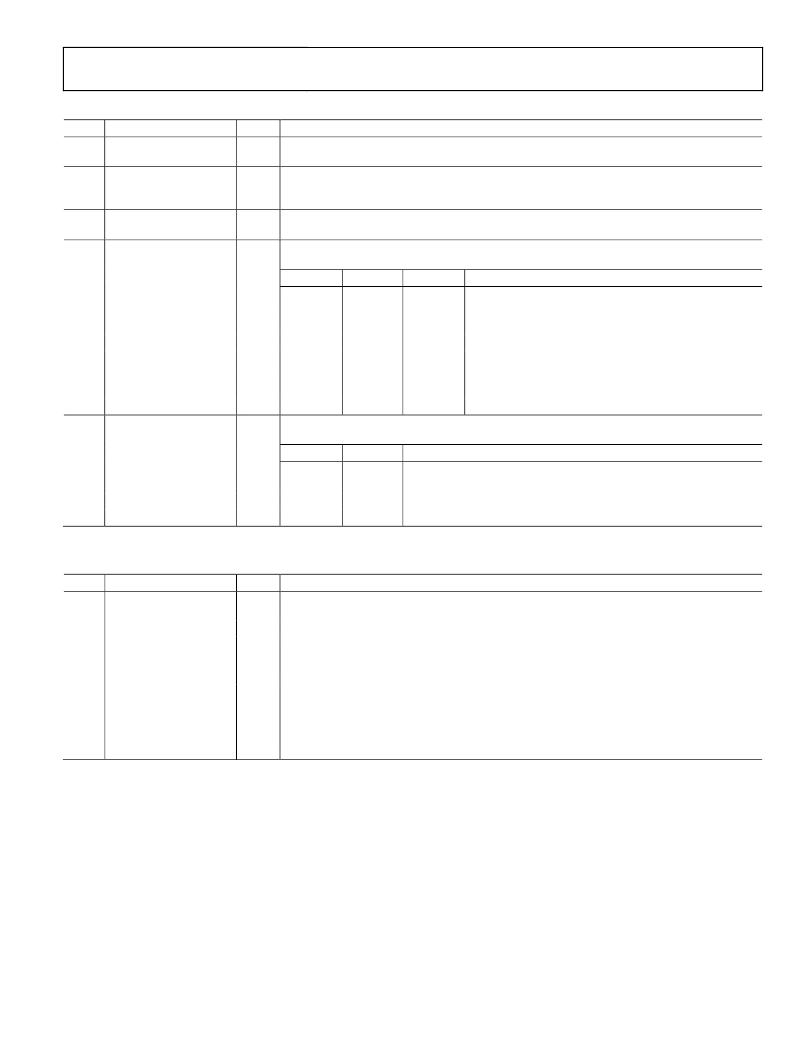

�Table 15. Register 0x0F—Soft Start Blan� k� Fault� Flags� Register�

�Bits�

�7�

�Name�

�Blank� SR�

�R/W�

�R/W�

�Description�

�Setting� this� bit� means� that� the� SR1� and� SR2� PWM� outputs� are� not� enabled� until� the� end� of� the�

�soft� start� ramp� time.�

�6�

�5�

�4�

�3�

�2�

�Blank� OTP�

�Blank� FLAGIN�

�Blank� local� OVP�

�Blank� load� OVP�

�Blank� CS2� accurate� OCP�

�R/W�

�R/W�

�R/W�

�R/W�

�R/W�

�Setting� this� bit� means� that� the� OTP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� FLAGIN� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� local� OVP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� load� OVP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Setting� this� bit� means� that� the� CS2� accurate� OCP� flag� is� ignored� until� the� end� of� the� soft� start�

�ramp� time.�

�1�

�Blank� CS1� accurate� OCP�

�R/W�

�Setting� this� bit� means� that� the� CS1� accurate� OCP� flag� is� ignored� until� the� end� of� the� soft� start�

�ramp� time.�

�0�

�Blank� CS1� fast� OCP�

�R/W�

�Setting� this� bit� means� that� the� CS1� fast� OCP� flag� is� ignored� until� the� end� of� the� soft� start� ramp� time.�

�Rev.� 0� |� Page� 37� of� 72�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADP1046-100-EVALZ

BOARD EVAL FOR ADP1046-100

ADP1048-600-EVALZ

BOARD EVAL ADP1048-600

ADP190CB-EVALZ

BOARD EVAL ADP190

ADP191CB-EVALZ

EVAL BOARD FOR ADP191

ADP194CB-EVALZ

BOARD EVAL FOR ADP194ACBZ

ADP195CP-EVALZ

BOARD EVAL FOR ADP195ACPZ

ADP197CB-EVALZ

BOARD EVAL FOR ADP197ACBZ

ADP198CP-EVALZ

BOARD EVAL FOR ADP198

相关代理商/技术参数

ADP1043AIF300EVALZ

制造商:Analog Devices 功能描述:ADP1043A 300W EVALUATION BOARD - Boxed Product (Development Kits)

ADP1043A-USB-Z

功能描述:EVAL BOARD DIG POWER SUPPLY RoHS:是 类别:编程器,开发系统 >> 配件 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program RoHS指令信息:IButton RoHS Compliance Plan 标准包装:1 系列:- 附件类型:USB 至 1-Wire? RJ11 适配器 适用于相关产品:1-Wire? 设备 产品目录页面:1429 (CN2011-ZH PDF)

ADP1043-EVALZ

制造商:Analog Devices 功能描述:EVALUATION BOARDS - Bulk

ADP1043FB100-EVALZ

制造商:Analog Devices 功能描述:ADP1043 100W EVALUATION BOARD

ADP1045ACPZ-RL

制造商:Analog Devices 功能描述:

ADP1046

制造商:AD 制造商全称:Analog Devices 功能描述:Digital Controller for Isolated

ADP1046-100-EVALZ

功能描述:BOARD EVAL FOR ADP1046-100 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板

ADP1046A

制造商:AD 制造商全称:Analog Devices 功能描述:Digital Controller for Isolated Power Supply Applications